Variance Maximization

This project demonstrates the proof-of-concept for FPGA-intrinsic

analog evolvable hardware

on the Lattice iCE40hx1k.

Description

Among the simplest fitness functions to implement for FPGA intrinsic analog evolvable hardware is the variance maximization function. Plainly put, this function demands the maximum change, either positive or negative, of each instantaneous measurement from the microcontroller. The ultimate effect is that the amplitude of the output waveform will increase with each successive generation.

| Runtime | Population | Generations | Mutation | Crossover |

|---|---|---|---|---|

| 4 - 5 hours | 50 | 100 | 0.005 | 0.5 |

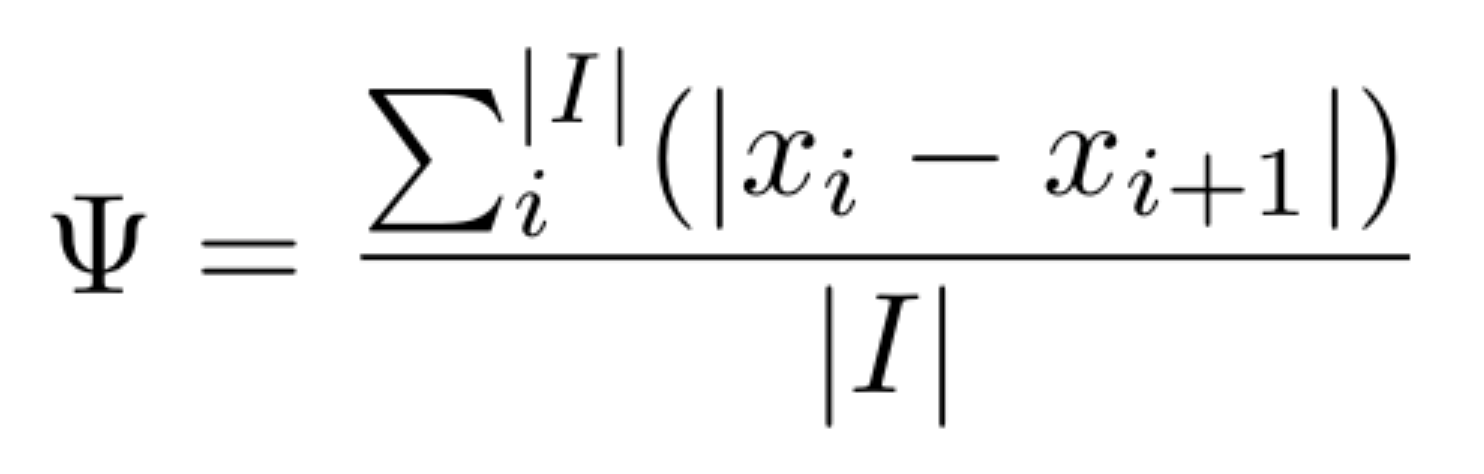

Fitness Function

|

This fitness function sums the absolute difference for each analog-to-digital (ADC) sequentially sampled pair-wise input from the microcontroller and divides it by the length of samples. Using default parameters, this adds averages all signal differentials for a single circuit. Doing this for and entire population yields a circuit with maximal amplitude/variance. |

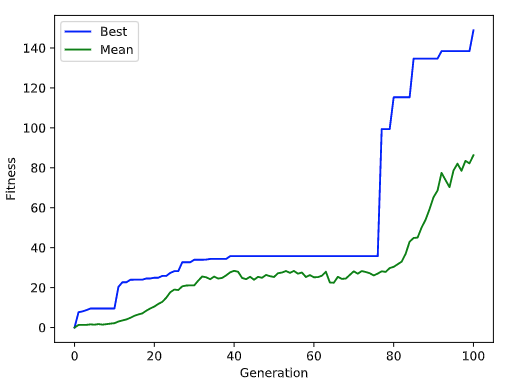

Results

|

Given that this is a real-world, physical system, results are strongly dependent on the natural stochastic noise present within and around the device. However, the plot depicted here illustrates an example of what kind of evolutionary progress one can expect when executing the program using the default parameters. The initial population begins with a very low fitness (single digit), before making a steady climb to a local optima. Following a sufficient amount of search time, a new optima is established and the population begins to climb in fitness. Because the default parameter for [generations] is set to 100, the algorithm terminates search. It is possible to achieve an even higher fitness with longer search duration. |